# Single-package 5GHz WLAN RF module with embedded patch antenna and 20dBm power amplifier

Julien Ryckaert, Steven Brebels, Boris Come, Wim Diels, Dries Hauspie, Serguei Stoukatch, Kristof Vaesen, Walter De Raedt, Stephane Donnay

IMEC, Kapeldreef 75, 3001 Leuven, Belgium

**Abstract** — The demanding requirements of emerging telecom standards compel designers to conceive transceivers that integrate building blocks designed in different technologies. Such heterogeneous systems, together with the need for miniaturization, require packaging and integration techniques more involved than all current reported work. By combining a thin-film technology on a glass substrate (MCM-D) with laminates for the ball grid array (BGA) package, we can integrate, in a single package, a 5GHz WLAN RF module. The package includes a BiCMOS IC, a GaAs power amplifier (PA) with 20dBm output compression [1], a GaAs TX/RX switch with 1dB insertion loss [2], high-quality integrated RF filters and a patch antenna with more than 80% efficiency.

## I. INTRODUCTION

Emerging telecom standards promise the user ever more attractive performances. The real challenge however is to realize attractive solutions for these complex systems. For WLAN applications, integrated solutions realized in a complete MMIC technology have recently been demonstrated [3,4] but they suffer from the high production cost of these technologies. Recent advances in modern silicon technologies now allow Zero-IF and low-IF architectures to be used in radio systems [5]. The dream of a fully integrated radio system, avoiding the expensive external SAW filters, slowly turns to become a reality. However, the road towards a system fully integrated on a single chip (SoC) still contains pitfalls in order to meet the performances expected from high-end applications such as WLAN. For instance, the maximum output power to be delivered by the PA still remains a critical issue. Some other elements of the front-end, like the TX/RX switch, the RF filters or the VCO tank, may also be hard to be implemented in standard silicon technologies. Even front-end works previously endeavored in full CMOS are now moving towards heterogeneous systems with external components [6]. This all means that one needs to find an optimal way to integrate these critical external components in a single package while keeping the cost and the size of the system as low as possible.

In this work, we present a System-in-a-Package (SiP) approach allowing the integration of the full system in a

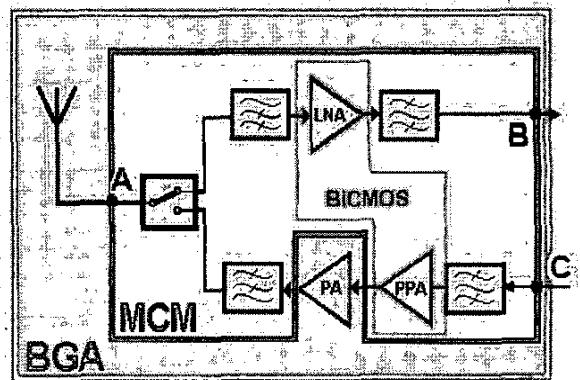

single package, using elements realized in different technologies. The antenna has also been integrated in the module and shows better performances than any other solution ever reported in the literature [7,8]. To prove our concept, we have chosen to integrate the first section of a traditional WLAN RF front-end. A block diagram is shown on Fig. 1. In this package, we have integrated a GaAs PA, a GaAs TX/RX switch, high-quality RF MCM-D filters, and a patch antenna together with a BiCMOS IC containing the low-noise amplifier (LNA) and the power pre-amplifier (PPA).

Fig. 1. Block diagram of the system

The paper is organized as follows. The next section discusses the assembly of the BiCMOS IC and the TX/RX switch on the MCM-D module where the different RF filters are also implemented (Fig. 1.). In the third section, we explain how the module is further mounted on a ball grid array (BGA) package together with the power amplifier and the patch antenna. The overall system performances are presented in the fourth section, followed by conclusions in the last section of the paper.

## II. INTEGRATION OF THE BiCMOS CHIP WITH THE MCM-D MODULE

MCM-D is a thin-film interconnection technology with high-quality integrated passives, where chips can be mounted through a flip-chip technique [9]. The MCM-D

technology consists of one aluminum layer and two copper layers alternating with dielectric layers of benzocyclobutene (BCB,  $\epsilon_r=2.7$ ). Inductors with quality factors up to 100 at 10GHz,  $Ta_2O_5$  capacitors up to 1nF and a wide range of coplanar waveguides can be realized in these layers. The lithographic nature of this thin-film technology guarantees low tolerances due to process variations [9] (1% on inductors and 5% on BCB capacitors).

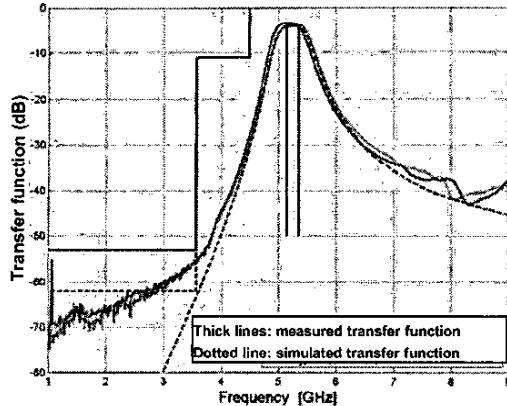

The high-quality RF filters are designed in this technology and do not require any trimming. Fig. 2. shows the highest shifts in the measured transfer function of the band-pass filter. The filter specification mask and the simulated results are also shown on the figure.

Fig. 2. Measured transfer function of the bandpass filter in the highest frequency shifts as compared to simulations.

In the receive path, the filtering consists of a 0.8dB-loss 2-LC-section highpass filter before the LNA to reject the low-frequency blockers, and a 4dB-loss 3-LC-section bandpass filter (BPF) after the LNA that provides the required image rejection at the downconverter input, for down-conversion to an intermediate frequency at 900MHz. In the transmit chain a similar BPF is used before the PPA and a 0.8dB-loss 2-LC-section lowpass filter after the PA.

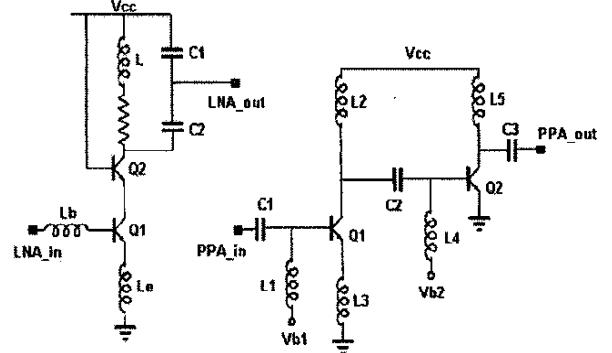

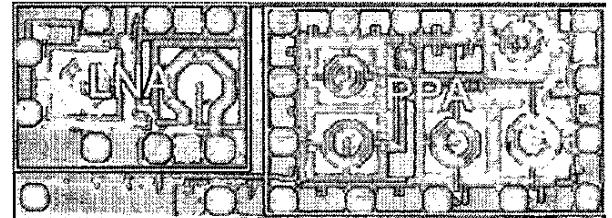

The MCM-D module is also used as an interconnection medium for the different blocks. The GaAs switch and the BiCMOS chip are mounted on the module. The GaAs switch is a commercial component that features 1.1dB of insertion loss, 38dB of isolation and a 1dB compression point at 27dBm input power, specifications which are difficult to achieve on a Si chip. The BiCMOS chip is realized in a 0.35um SiGe technology. It consists of an LNA and a PPA. The circuit schematics are shown in Fig. 3. The LNA is a cascode-type amplifier with the input matching inductor on the MCM-D for better noise figure performance. All other inductors of the LNA and PPA are

integrated on chip. The LNA has a measured gain of 12dB and a noise figure of 2.5dB. The PPA is a two-stage class A amplifier. Its measured gain is 16.5dB with 13dBm output compression. The current consumption of these two circuits is 5mA and 20mA respectively from a 3V supply. Fig. 4. shows the microphotograph of the chip.

Fig. 3. Schematic of the cascode LNA and the two-stage class A PPA

Fig. 4. Microphotograph of the BiCMOS IC

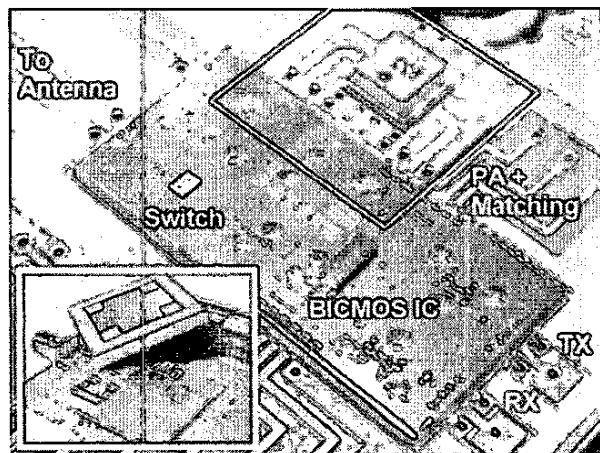

### III: BGA ASSEMBLY

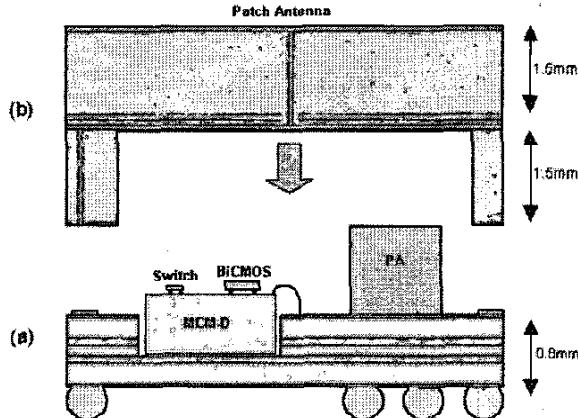

The MCM-D substrate carrying the BiCMOS chip is mounted on a 0.8mm thick BGA via bondwires together with a flip-chip mounted packaged GaAs PA. A cavity is formed in the BGA to reduce the length of the bondwires to the MCM-D. Their measured insertion loss is lower than 0.4dB at 5GHz. A cross-section of this package is illustrated on Fig. 5. and a picture of the complete module is presented on Fig. 10. The overall dimension of the module is 30x30x4.3mm<sup>3</sup>.

The BGA technology consists of 4 copper metal layers and 3 RO4003 dielectric layers ( $\epsilon_r = 3.38$ ). The ball connections to the PCB modify the electrical properties of the system and must be compensated for on the BGA itself. After compensation, the measured insertion loss of these balls is lower than 0.1dB at 5GHz. The power amplifier is a packaged GaAs commercial component with an output 1dB compression point of 20dBm. The PA requires an external matching network, which has been realized on the MCM-D substrate. The PA has been characterized separately on a dedicated BGA with its

matching network; the measured gain is 6.5dB and the output 1dB compression point is 20dBm. It consumes 140mA from a 5V supply. The PA should not be mounted directly on the MCM-D module, as the glass substrate is a thermal insulator. Sixteen thermal vias in the vicinity of the PA have been added on the BGA.

Fig. 5. Cross-section of the complete BGA package. The antenna laminate encapsulates the BGA, which contains the MCM-D module and the PA

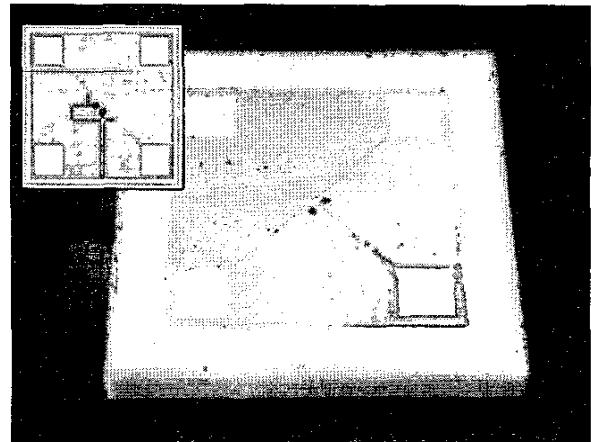

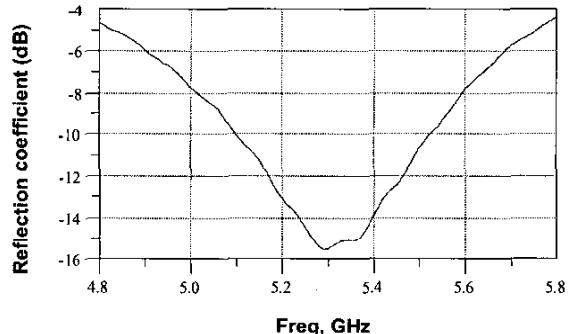

The antenna is a square patch antenna with circular polarization. The square patch layout (Fig. 6.) is cut at selected places to realize a more wideband current distribution on the patch, while radiating with a high efficiency [10,11]. The antenna is fed by two orthogonal quadrature signals to realize a circular polarization. The simulated efficiency is better than 80%. The measured reflection coefficient of the antenna (Fig. 7.) is below -10dB over the 5.15-5.35GHz frequency band of the IEEE802.11a standard. The antenna is realized on a similar laminate (Fig. 5.). This laminate is mounted as a cap on the first BGA and a 1.5mm cavity is machined in the laminate bottom-layer to encapsulate the PA and the MCM-D module.

The total thickness of 4.3mm is largely determined by the thickness of the antenna and the thickness of the PA package. The former forms the top layer of the cap. It is dictated by the required dielectric thickness to have good radiation efficiency for the patch-antenna (1.5mm), given the dielectric constant of the laminate material. The latter however, which determines the thickness of the bottom layer of the cap, could be easily reduced from 1.5mm to a few tenths of mm by using a bare-die PA. We were prevented from doing so due to availability issues.

The other dimensions of the package are limited by the size of the patch of the antenna. Compacter patch-antennas are possible, but the antenna implemented in this work exhibits a high axial-ratio and almost 400MHz bandwidth.

Fig. 6. Picture and layout of the slotted patch antenna.

Fig. 7. Measured reflection coefficient of the patch antenna.

#### IV. SYSTEM PERFORMANCES

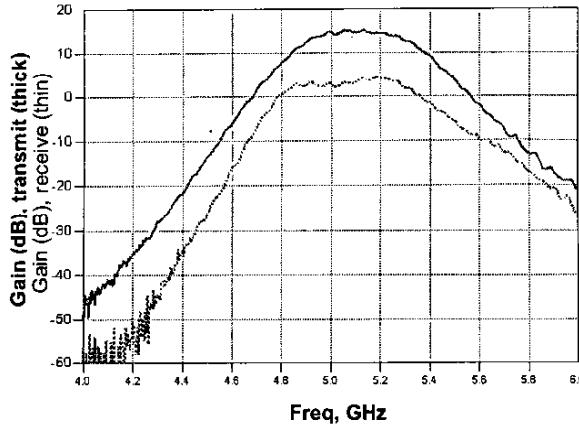

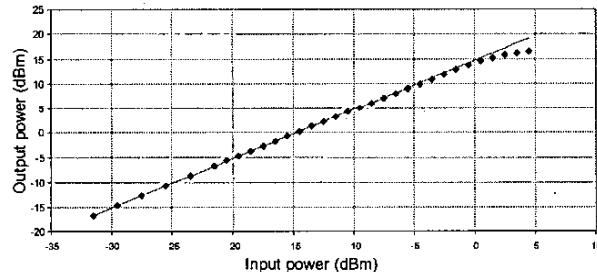

This module is to be implemented into a superheterodyne transceiver for WLAN applications. The measurement results of the module are presented on Fig. 8. In receive mode, the gain of the chain from the antenna connector (A on Fig. 1.) to the RX output (B on Fig. 1.) is 4dB with a noise figure of 6dB. Measurements on the transmit chain from the TX input (C on Fig. 1.) to the antenna connector (A on Fig. 1.) show 14.7dB gain (Fig. 8.) with a compression at the antenna connector of 15.5dBm (Fig. 9.). These figures correspond to the system specifications derived for the complete transceiver study aiming at compliance with IEEE and ETSI standards.

It should be noted that the combined PPA and PA reach their compression point simultaneously, which degrades the overall linearity. Furthermore, this Watkins-Johnson PA [1] has its optimum performance in the 900MHz band, which explains its low gain at 5GHz. When we started this work, it was the available commercial component best fitted for this SiP approach. A PA with higher gain and similar output compression would substantially improve

the linearity of the transmit chain. We are currently replacing the W-J PA by another commercial PA with higher gain targeted for 5Ghz WLAN products. A higher output power with a more compact package is expected.

Fig. 8. Measured transfer characteristics from point C to point A and from point A to point B on Fig. 1. Thick line for transmit mode and thin line for receive mode.

Fig. 9. Measured output power versus the input power of the complete transmit chain (point C to point A on Fig. 1.)

Fig. 10. Photograph of the BGA package. The PA has an MCM-D matching network. The inset shows the 2 parts of the RF module with the slotted patch antenna.

## V. CONCLUSION

In our SiP approach, we show that a PA, a patch antenna and MCM-D filters can be integrated together with a silicon IC. This work paves the way to system-in-a-package assembly of complete radios containing a BiCMOS IC for most of the RF blocks and off-chip components for the critical ones, together with a modem realized in a standard CMOS technology. It is an important step towards a complete SiP that includes the front-end as well as the digital part of the transceiver.

## ACKNOWLEDGEMENTS

The authors thank Michael Libois and Hans Suys for their technical support.

## REFERENCES

- [1] Watkins-Johnson, 0.25-6GHz Power Amplifier, AH4, [www.watkins-johnson.com/pdf/ah4.pdf](http://www.watkins-johnson.com/pdf/ah4.pdf)

- [2] Agilent Technologies, DC-8GHz SPDT Switch, HMMC-2007, [literature.agilent.com/litweb/pdf/5988-3198EN.pdf](http://literature.agilent.com/litweb/pdf/5988-3198EN.pdf)

- [3] C-H Lee et al., "Broadband highly integrated LTCC front-end module for IEEE 802.11a WLAN applications", *IEEE Microwave Symposium Digest*, 2002 IEEE MTT-S International vol.2 pp 1045-1048.

- [4] S. Pinel et al., "3D integrated LTCC module using  $\mu$ BGA technology for compact C-band RF front-end module", *IEEE J. Microwave Symposium Digest*, 2002, pp. 1553-1556.

- [5] D. Su et al., "A 5GHz CMOS Transceiver for IEEE 802.11a Wireless LAN", *International Solid-State Circuit Conference*, 2002, Paper 5.4, Vol.1, pp 92-449.

- [6] B. McFarland , A. Shor, A. Tabatabaei, "A 2.4 & 5 GHz dual band 802.11 WLAN supporting data rates to 108 Mb/sb" *Gallium Arsenide Integrated Circuit Symposium*, 2002, 24th Annual Technical Digest , 2002, pp. 11 -14.

- [7] J. Zhao, S. Raman, "An integrated chip-scale active antenna for 5-6 GHz wireless Microsystems", *IEEE RAWCON*, 2002, pp 149 -152.

- [8] Y.P. Zhang, "Integration of Microstrip Patch Antenna on Ceramic Ball Grid Array Package", *Electronics Letters*, 2002, 38, pp 207-208.

- [9] S. Donnay et al., "Chip-package Codesign of a Low-Power 5-GHz RF front-End", *Proc. of the IEEE*, Oct. 2000, pp. 1583-1597.

- [10] J.R. James, P.S. Hall and C. Wood, "Microstrip Antenna Theory and Design", *IEE Electrom. Wave Series 12*, Londen, Peter Perigrinus, 1981.

- [11] S. Brebels et al., "The Antenna: Cornerstone for System-on-Package Integration of Future Wireless Systems", *Belgian Journal of Electronics and Communications*, 1, 2002.